## **Energy Efficiency of Computing Architectures**

A Deep Dive into Processors and Emerging Computing Machines

**Olivier Sentieys** Inria Univ. Rennes, Irisa

olivier.sentieys@inria.fr

http://people.rennes.inria.fr/Olivier.Sentievs

## Cairn Team at a Glance

- ~35 people, Rennes and Lannion campuses

- INRIA, Univ. Rennes 1, ENS Rennes

- Electrical Engineering & Computer Science

- Domain-specific computing architectures

- Design tools and compilers

- · Wireless, signal, image, security

2

## **Energy Efficiency Challenges**

- Teraops/Watt?

- $-10^{12}$  op./s/W  $\equiv 1$  pJ/op

- Several orders of magnitude from current processors and multicores

- From Sensors > to Clouds

■ 1 TOPS @ 1W

- 1 GOPS @ 1mW

- Clouds, embedded systems

- IoT sensor nodes

## Improving Energy Efficiency

- Technology?

- What can advanced technology nodes bring

- Accelerate

- Energy advantages of specialized hardware

- Approximate

- Playing with accuracy to reduce energy

- Manage the Power

- Dynamic Voltage/frequency (Over-)Scaling

- Energy Harvesting sensor nodes

## **Key Questions**

- A deep dive into processors... (I hope not too deep)

- Basics on transistors, logic gates, registers, memory

- Energy consumption of processor core/uncore

- Computers are parallel

- Billions of transistors doing the job at the same time

- Are multicore processors the solution?

- Specializing the computer

- Reconfigurable computing

- Emerging paradigms

- Neuromorphic, approximate, stochastic

## Outline

- · Part I: From Transistors to Logic Gates

- Basic Element, Delay, Power Consumption

- The Issue of Synchronization

- Part II: Inside a Processor

- Von-Neumann Architecture, Instruction Set Architecture, Operating Systems

- Multicore Processors, Power and Utilization Walls

- · Part III: Pushing the Accelerator!

- Hardware Accelerators

- Reconfigurable Computing

- Part IV: Emerging Computing Paradigms

- Neuromorphic Computing

- Approximate Computing

- Chips are going 3D

6

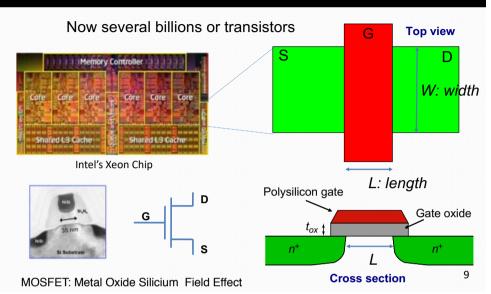

## Integrated Circuit Design

• Chips, logic gates and transistors

Intel's Xeon Chip

## Part I: From Transistors to Logic Gates

- The Fundamental Element: MOSFET Transistor

- Design of CMOS Cells: Combinatorial Logic

- Memory Cells

- Delay and Power Consumption

- Synchronous Design

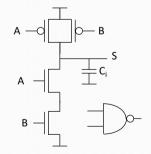

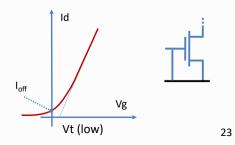

## Fundamental Building Block: **MOSFET Transistor**

## The Basic Element: Transistor

Transistor as a switch

- Vgs > Vt: NMOS on - Resistance R<sub>DS</sub>

- - Vgs < Vt: NMOS off - Leakage I<sub>off</sub>

Vt: threshold voltage

Ids

- Gate: capacitance C<sub>G</sub>

- Switch: resistance R<sub>DS</sub>

10

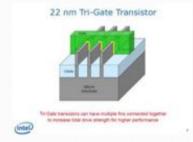

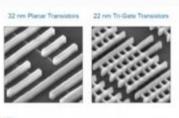

## **Transistors Nowadays**

• Intel FinFET: transistors go 3D

Fully Depleted SOI<sup>1</sup> Low-power

<sup>1</sup>Silicon on Insulator

## Part I: From Transistors to Logic Gates

- The Fundamental Element: MOSFET Transistor

- Design of CMOS Cells: Combinatorial Logic

- Memory Cells

- Delay and Power Consumption

- Synchronous Design

11

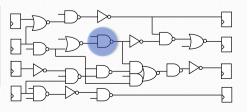

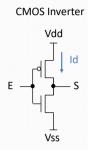

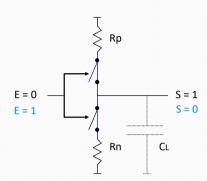

## Combinatorial Logic Cells

Complementary Logic (CMOS)

13

15

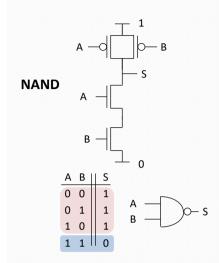

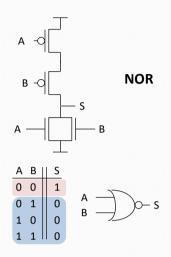

## NAND and NOR

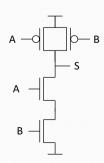

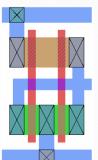

14

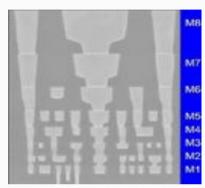

## **Layout Design**

#### Silicon

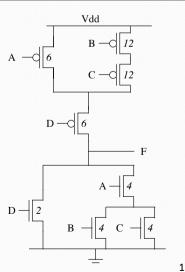

## Complex Gates

- $F = \overline{A.(B+C)+D}$

- The art of transistor sizing

- Equilibrate delay for  $0 \rightarrow 1$ and  $1 \rightarrow 0$  output transitions

- Minimize cell area

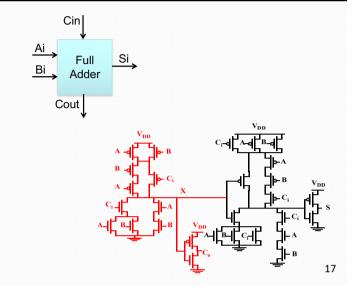

## Complex Gates: Full Adder

Full Adder

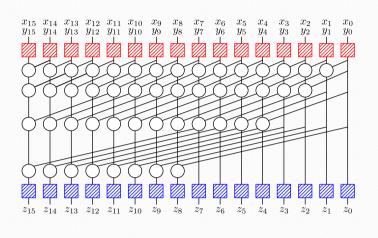

## **Complex Functions**

• 16-bit Adder (integer)

18

## Part I: From Transistors to Logic Gates

- The Fundamental Element: MOSFET Transistor

- Design of CMOS Cells: Combinatorial Logic

- Memory Cells

- Delay and Power Consumption

- Synchronous Design

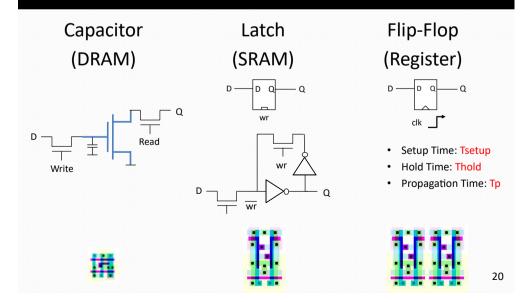

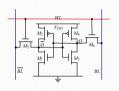

## **Storing Values**

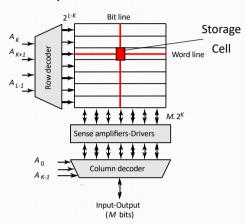

## Memory

- L2 Cache contains 4 Millions SRAM cells

- Raw/column of 2000 cells

21

## **Delay: Parasitic Elements**

- Drain-Source Resistance:  $R_{DS} = \frac{L}{W} \frac{1}{k(V_{dd} V_t)}$

- Gate Capacitance:  $C_g = \frac{\epsilon W.L}{t_{ox}} = W.L.C_{ox}$

Delay

$$\propto R_{DS}.C_g \propto \frac{L^2}{Vdd-Vt}$$

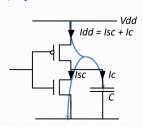

## **Power and Energy Consumption**

- Dynamic power

- Charge and discharge of node capacitance

- Energy =  $C.Vdd^2$

- Power

$\mathbf{P_{dyn_i}} = \mathbf{C.Vdd^2.f.Prob_{0 o 1}}$

- Static power: Ps

- Sub-threshold and junction leakage current

$$P_{stat_i} = N.I_{off}.Vdd \\$$

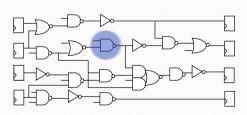

## Power at Higher Level

· Propagating activity

$$\mathbf{P} = \sum_{\mathbf{i}} \left[ \alpha_{\mathbf{i}}.\mathbf{f_{i}}.\mathbf{C_{i}}.\mathbf{V}dd^{2} + \mathbf{I_{leak_{i}}}.\mathbf{V}dd \right]$$

24

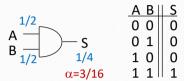

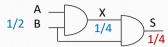

## Activity

- Activity α<sub>i</sub> is the probability to have a 0→1 transitions at the output of a gate

- Example: AND gate

$$-P_S = P(S=1) = P_A P_B$$

$$-\alpha_i = P_S(1-P_S)$$

Activity propagation

25

27

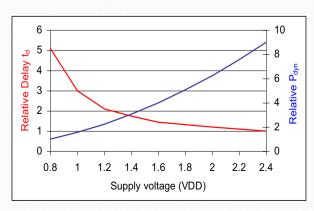

## Dynamic Power vs. Performance

• Decreasing Vdd reduces power but increases delay  $P_{dyn_i} = \alpha_i.f_{clk}.C_i.Vdd^2$

$$Delay \propto \frac{1}{V_{dd} - V_t}$$

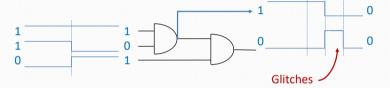

## Propagating Activity is not So Simple

Conditional probabilities

- Glitches: gate delay

- Significant in arithmetic

26

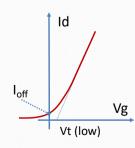

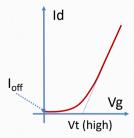

## Leakage vs. performance

• High performance

$P_{\mathbf{stat_i}} = N.I_{off}.Vdd$

$$Delay \propto \frac{1}{V_{dd} - V_t}$$

Low leakage

loff:

- Exponential in inverse of Vt

- Exponential in temperature

- Linear in device count

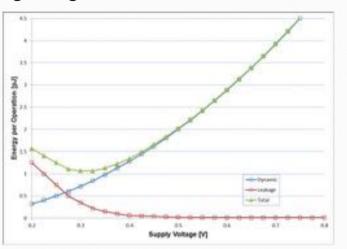

## Minimum Energy per Operation

Putting all together

## On-Chip Interconnect?

- Gate delay decreases but... wire delay increases

- Crossing chip in 5-10 clock cycles

- Also affected by noise...

- Metal layers to reduce wire delay

- Repeaters

- Towards networkon-chip

30

## **Conclusion: Power in CMOS**

$$P = \sum_{i} \left[ \alpha_{i}.f_{i}.C_{i}.Vdd^{2} + I_{leak_{i}}.Vdd \right]$$

- Dynamic power

- 40-70% today

- Decreasing relatively

- DVFS becomes more and more difficult

- Leakage power

- 20-50 % today

- Increasing rapidly

- number of transistors

- Vdd/Vt scaling

- Critical for memory

$$P = \frac{energy}{operation} \times rate + static\ power$$

# Inside (Simple) Processor Architecture

36

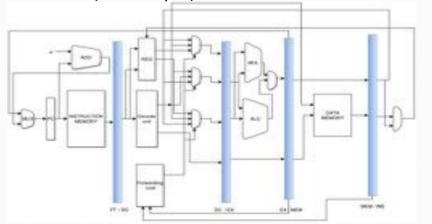

## **Von Neumann Computers**

- Processing address, data, control, on the same resources

- Single memory for data and program

- Sequential behavior

- Practically, most processors use Harvard model: separated data and program memory

37

41

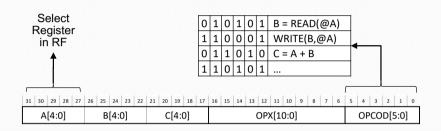

## Instruction Set Architecture (ISA)

- ISA defines a programmer's interface

- Each instruction is defined by coding (binary) and semantics

40

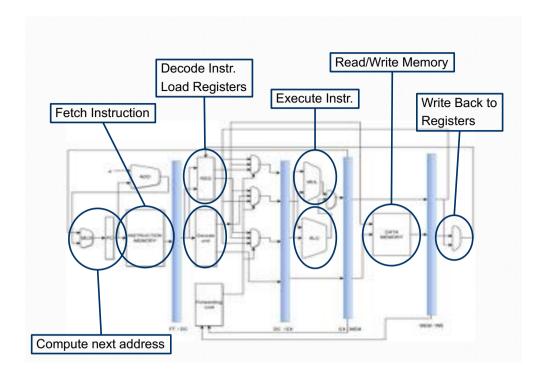

## Microarchitecture Pipeline

Microarchitecture defines how instructions are executed (not unique)

## Execution of an instruction involves

- 1. Instruction fetch

- 2. Decode and register fetch

- 3. ALU operation

- 4. Memory operation (optional)

- 5. Write back (optional) and compute address of next instruction

## Achieving Higher Performance

- Branch/value prediction

- Cache memory

- In-core parallelism

- Multiple Fus

- Out of order execution

- VLIW+good compilers

- Multiple cores on a single chip

## **Abstraction in Computer Systems**

• Maximum of an array T

#### numpy.amax(T)

| <pre>int largest(int T[], int length) {</pre>      |

|----------------------------------------------------|

| <pre>int max = T[0];</pre>                         |

| for(i=1; i <length; i++)="" td="" {<=""></length;> |

| if (max < T[i]) {                                  |

| <pre>max = T[i];</pre>                             |

| }                                                  |

| }                                                  |

| return max;                                        |

| }                                                  |

| 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

|      | R1 ← *R2  | // max |

|------|-----------|--------|

| loop | R2 ← R2+1 | // T[] |

|      | R3 ← *R2  |        |

|      | R1 < R3 ? |        |

|      | BZ next   |        |

|      | R1 ← R3   |        |

| next | B loop    |        |

|      |           |        |

45

## Abstraction and Performance?

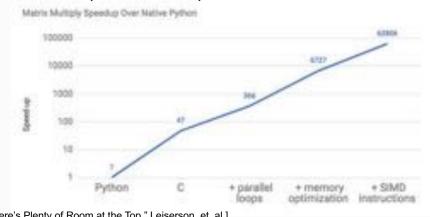

• Matrix Multiply: relative speedup to a Python version (18 core Intel)

["There's Plenty of Room at the Top," Leiserson, et. al."

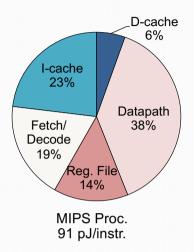

## **Energy Cost in a Processor**

#### • Operation:

- 32-bit addition: 0.05pJ

- 16-bit multiply: 0.25pJ

- 64-bit FPU: 20pJ/op

#### Instruction:

fetch, decode, read 2

operands from RF, execute, write back

49

## **Energy Cost in a Processor**

Fetching operands costs more than computing

50

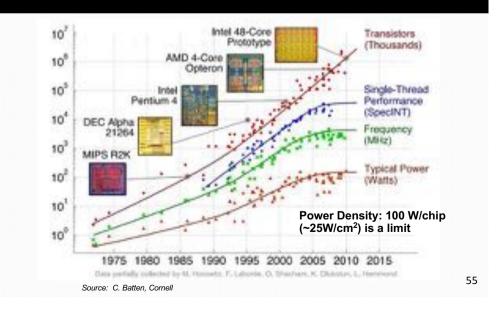

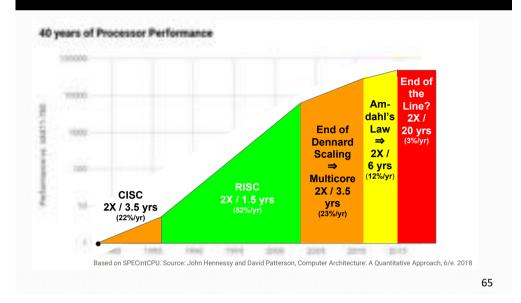

## And then came the "Power Wall"

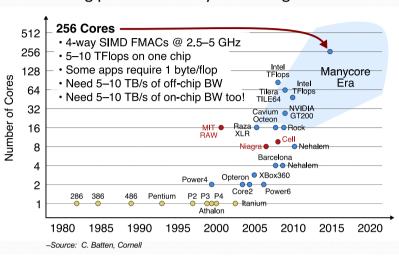

## Multicore: it's all a trick! Power and Utilization Walls

## and the "Multicore Era"

Increasing performance by increasing # of cores

## Moving to multicore

1 core@2GHz@1.2V@1W

1W 2GHz 1.2V

1 core@1GHz@0.8V@0.25W

0.22W 1GHz 0.8V

2 cores@1GHz@0.8V@0.5W

1GHz

• But... twice area (and not so simple)

1GHz

Advanced technology nodes?

62

#### **Technology Scaling** End of Dennard's Scaling

56

Energy efficiency is not scaling along with integration capacity

#### **Leakage limited scaling**

|                                 | _                |

|---------------------------------|------------------|

| Device count                    | S <sup>2</sup>   |

| Device frequency                | S                |

| Device power (cap)              | 1/S              |

| Device power (V <sub>dd</sub> ) | ~1               |

| Utilization                     | 1/S <sup>2</sup> |

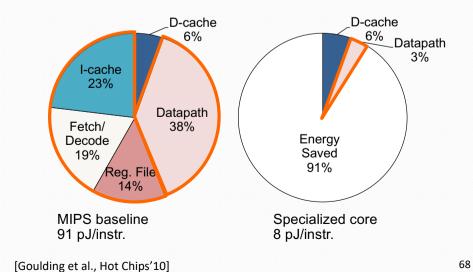

• Utilization Wall: percentage of a chip that can switch at full frequency drops exponentially

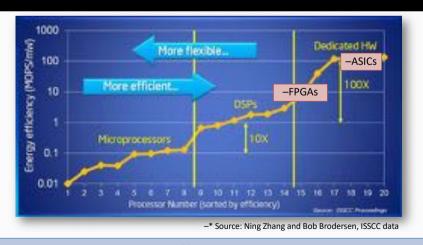

Replace dark cores with specialized cores (10-100x more energy efficient)

Capacitance, Vdd 1/S 1/S<sup>2</sup> Device power Utilization

Classical (Dennard's) scaling

28 nm

Device count

Device frequency

Core; 100W@f

20 nm

14 nm

Intel's Xeon Chip

## End of Growth of Speed?

## Part III: Pushing the Accelerator!

66

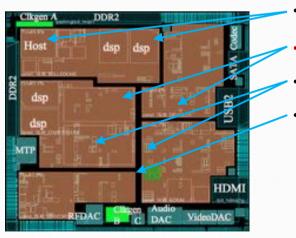

## What is a HW accelerator?

- 16 processors

- 38 HW blocks

- 140 memory blocks

- 5 Gbytes/s on-chip interconnection network

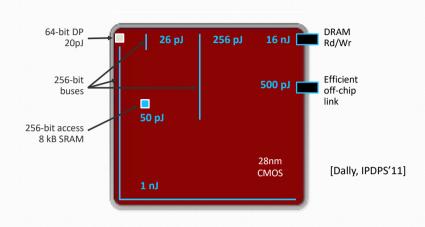

## **Energy Savings in Specialized HW**

## An example: Bitcoin Mining

| Туре | Model                   | Mhash/s   | Mhash/J | Power (W) |

|------|-------------------------|-----------|---------|-----------|

| GPP  | Intel Xeon X5355 (dual) | 22.76     | 0.09    | 120       |

| GPP  | ARMCortex-A9            | 0.57      | 1.14    | 1.5       |

| GPP  | Intel Core i7 3930k     | 66.6      | 0.51    | 130       |

| GPU  | AMD 7970x3              | 2050      | 2.41    | 850       |

| GPU  | Nvidia GTX460           | 158       | 0.66    | 240       |

| ASIC | AntMiner S1             | 180.000   | 500     | 360       |

| ASIC | AntMiner S5             | 1.155.000 | 1957    | 590       |

| FPGA | Bitcoin Dominator X5000 | 100       | 14.7    | 6.8       |

| FPGA | Butterflylabs Mini Rig  | 25.200    | 20.16   | 1250      |

69

71

## Making ANN Inference more Efficient

- Main motivation: AlphaGo consumes around 250,000 Watts!

- Bring Logic and Memory closer

- · Compute less precisely

- Google Tensor Processing Units (TPU)

- Computations close to memory

- 8 bit operations

70

## The Efficiency of Specialization

-100-1000X Gap in Efficiency ... but Specialization comes with Penalties in Programmability

## Reconfigurable Hardware Accelerators

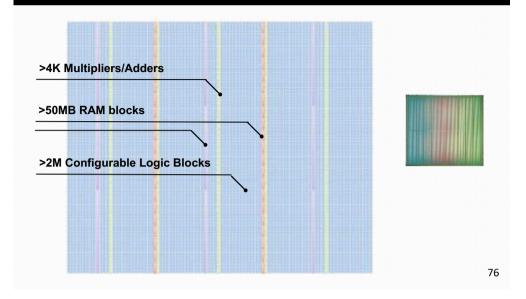

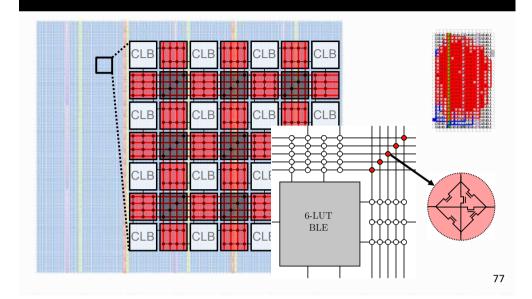

## Field Programmable Gate Array (FPGA)

## Field Programmable Gate Array (FPGA)

## The Program is the Configuration

## The Program is the Configuration

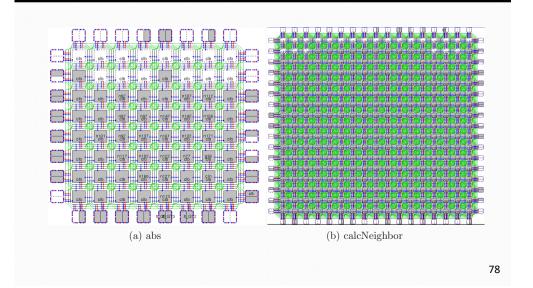

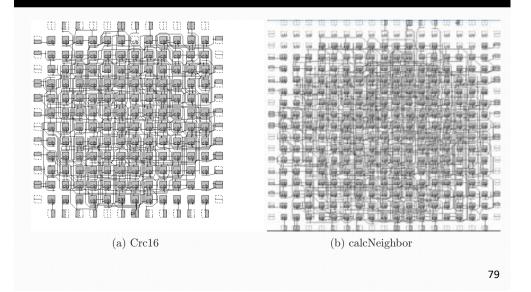

## **Space-Time Computation**

```

for(i=1; i<length; i++) {

if (max < T[i]) {

max = T[i];

}

}</pre>

```

```

for(i=1; i<N; i++) {

for(j=1; j<M; j++) {

y[i][j]+=x[i][j]*h[j][i]

}

}</pre>

```

80

82

## **FPGA Acceleration**

• FPGAs can run multiple tasks in parallel

FPGA accelerators for HPC/Cloud

• Towards heterogeneous multicores

81

## Amazon AWS EC2 F1

AWS EC2 F1 Platform

| Instance Size | FPGAs | DDR-4 (GiB) | vCPUs | Instance<br>Memory (GiB) | NVMe Instance<br>Storage (GB) | Network<br>Bandwidth |

|---------------|-------|-------------|-------|--------------------------|-------------------------------|----------------------|

| f1.2xlarge    | 1     | 4 x 16      | 8     | 122                      | 1 x 470                       | Up to 10 Gbps        |

| f1.16xlarge   | 8     | 32 x 16     | 64    | 976                      | 4 x 940                       | 25 Gbps              |

Up to 8 Xilinx UltraScale+ FPGA devices in a single EC2/F1 instance

## Time has Come for Specialization

- Microsoft Unveils Catapult to Accelerate Bing

- One FPGA per blade

- $-6 \times 8$  2-D torus topology

- High-end Stratix V FPGAs

- Running Bing Kernels for feature extraction and machine learning

- Increase ranking throughput by 95% at comparable latency to software-only

- Increase power consumption by 10%

- Increase total cost of ownership by less than 30%

# Part IV: Emerging Computing Paradigms

84

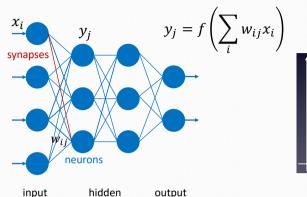

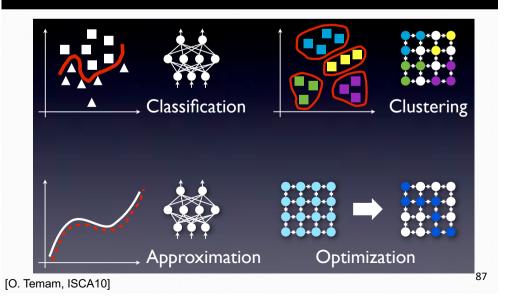

## How Do Artificial Neural Networks Work?

- Neural networks are not fundamentally complicated

- ullet The issue: finding the good weights with *learning*

### What ANNs Can Do

## So What's New?

## Convergence of trends

- Computer performance (e.g. GPU) can train neural networks with millions of weights

- Access to gigantic datasets

- Billions of images

- Training can take weeks!

- More complex ANNs

Imagenet

- Deep Convolutional Neural Networks (CNN)

- Long Short-Term Memory (LSTM) Recurrent Neural Networks

- Trendy vision applications

- Emerging technologies offer opportunities

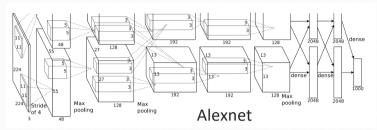

## So What's New?

Deeper Networks

Alex Krizhevsky *et al.*, Imagenet classification with deep convolutional neural networks, 2012.

91

## Complexity of Deep CNNs

- 10-30 GOPS

- Mainly convolutions

- 10-200 MB

- Fully-connected layers

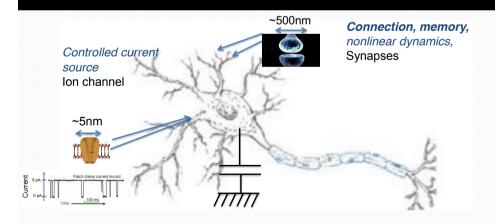

## And What About Energy?

The brain seems to have something very special about energy efficiency

20 Watt

AlphaGo (CPU+GPU with tree seach and deep neural networks)

>250 000 Watt

• Computers: arithmetic but chiefly memory transfers

## Real Biological Neurons

Brain computes with strong approximations (mostly analog) based on low power, slow, noisy and variable nano-devices

[D. Querlioz, CNRS]

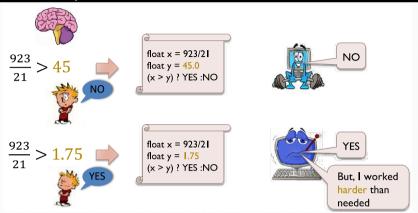

## Humans Approximate.... But Computers Do Not!

- Leads to inefficiency

- Overkill (for many applications)

## Many Applications are Error Resilient

- Produce outputs of acceptable quality despite approximate computation

- Perceptual limitations

- Redundancy in data and/or computations

- Noisy inputs

- · Digital communications, media processing, data mining, machine learning, web search, ...

e.g. Image Segmentation

94

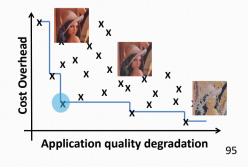

## **Approximate Computing**

- Play with approximations to reduce energy and increase execution speed while keeping accuracy in acceptable limits

- Relaxing the need for fully precise operations

- Design-time/run-time

- Abstraction levels

93

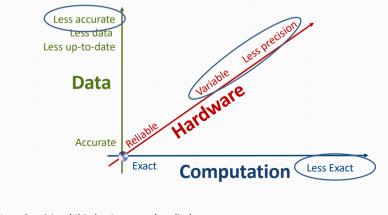

## **Approximate Computing**

Three dimensions to explore

Note: Precision (#bits) ≠ Accuracy (quality)

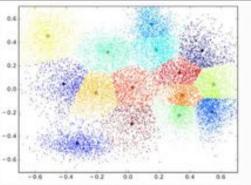

## K-Means Clustering

- Data mining, image classification, etc.

- A multidimensional space is organized as:

- -k clusters  $S_i$ ,

- $-S_i$  defined by its centroid  $\mu_i$

• Finding the set of clusters  $S = \{S_i\}_{i \in [0,k-1]}$  satisfying  $\underset{S}{\arg\min} \sum_{i=1}^k \sum_{x \in S_i} \|x - \mu_i\|^2$  is NP-hard (solved here by Lloyd's iterations)

97

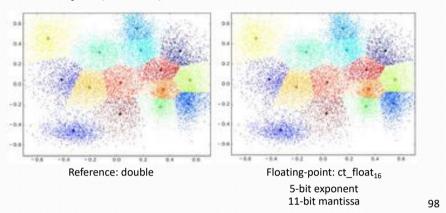

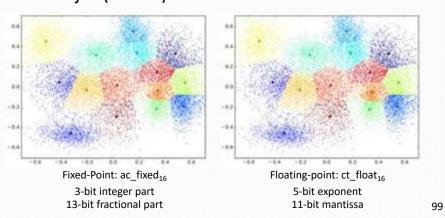

## **Approximate K-Means Clustering**

- W = 16 bits, accuracy = 10<sup>-4</sup>

- No major (visible) difference with reference

## **Approximate K-Means Clustering**

• W = 16 bits, accuracy =  $10^{-4}$

• No major (visible) difference with reference

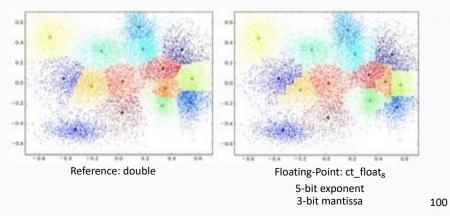

## **Approximate K-Means Clustering**

- W = 8 bits, accuracy = 10<sup>-4</sup>

- 8-bit float is still practical

## **Approximate K-Means Clustering**

• W = 8 bits, accuracy = 10<sup>-4</sup>

- 8-bit float is better and still practical

## Resilience

According to a rscheearch at Cmabrigde Uinervtisy, it doesn't mttaer in waht oredr the Itteers in a wrod are, the olny iprmoatnt tihng is taht the frist and Isat Itteer be at the rghit pclae. And we spnet hlaf our Ifie Iarennig how to splel wrods. Amzanig, no!

Our biological neurons are fault tolerant to computing errors and noisy inputs

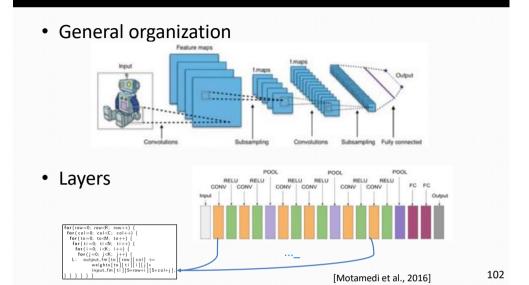

## **Deep Convolutional Neural Networks**

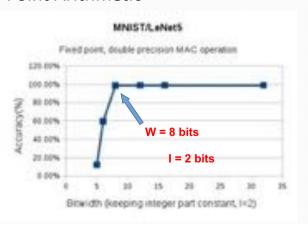

## **Approximate CNNs**

- 10k images, MNIST/Lenet

- Fixed-Point Arithmetic

## Summary

- Energy consun

- True in embed

- True in HPC, n

- End of Moore's law...

- Multicores but utilization wall

- Percentage of a chip that can switch at full frequency drops exponentially

105

## What's next?

- Emerging devices

- Cells, brain, neurons have "analog" behavior

- And compute with very low precision

- Making neuromorphic computing more efficient

Phase

Memristors, Oxide Resistive

Spin Torque Magnetic Memory

## What's next?

- Dark Silicon is also an opportunity

- Heterogeneous manycore architectures

- Efficiency of hardware specialization

- Domain-specific architectures and languages

- Computing just right

- @design-time or @run- time